学习笔记:运算放大器(OPA)超详细讲解(内含运用电路仿真)_爱学习的王大胖子的博客-CSDN博客 运算放大器的基础知识及常用芯片 - 知乎 (zhihu.com) 9.深入浅出:集成运放内部电路分析——参考《模拟电子技术基础》清华大学华成英主讲集成运放谁讲的比较好人生苦短我搞硬件的博客-CSDN博客

压摆率

us/V或者ns/ V 上升1V要的时间

参考增益带宽积

产生原因:运放内部寄生电容充放电

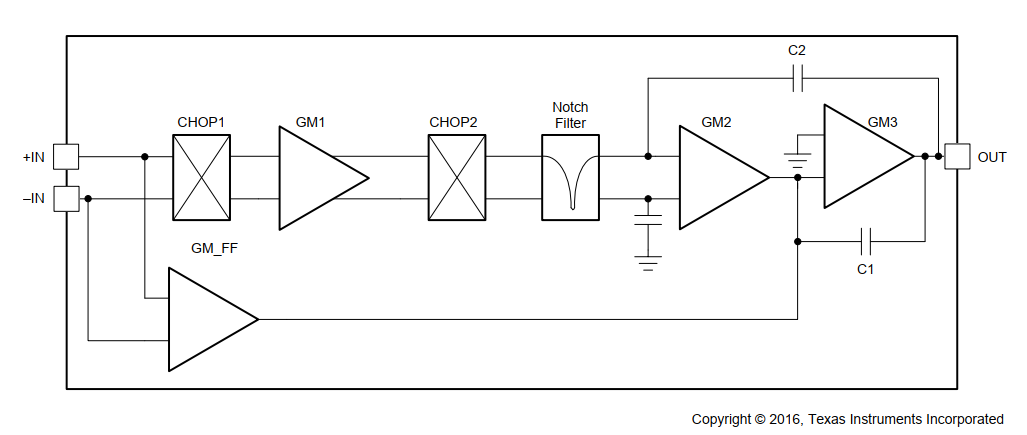

C1和C2

C1和C2

选值在增益带宽积计算频率的1/3左右

轨到轨

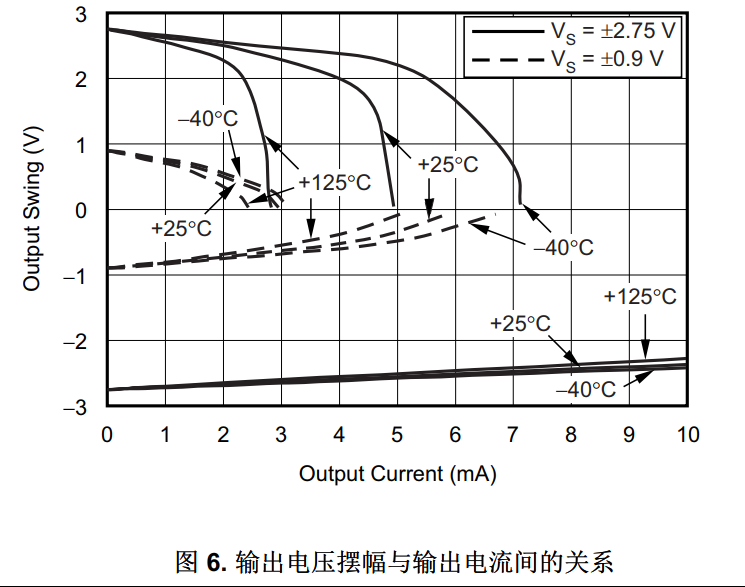

用了不是(虚假的)轨到轨的运放会摆幅不够 输入、输出信号都能到达两个电源轨 在实际条件下,并不能达到电源轨 来源输出MOS导通压降

输出摆幅

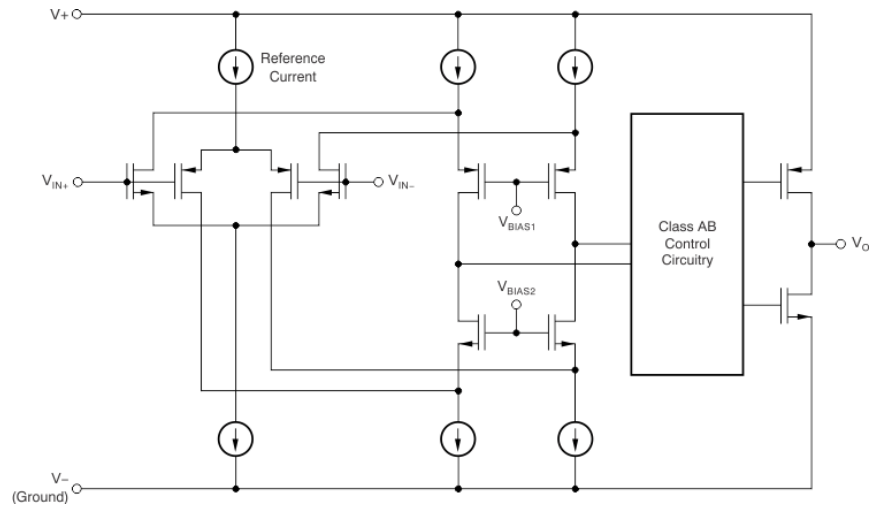

有些不是轨到轨运放:用NPN电流源、射极跟随器做输出级

Vo=Vs-I * Rds,输出级mos导通电阻产生压降

Vo=Vs-I * Rds,输出级mos导通电阻产生压降

这个图表示 I上升时压降越大,甚至上百 温度越高,导通电阻up 很少能偏到轨到轨 失真 影响信号质量

输入失调电压

为了使运放的输出电压等于0,必需在运放两个输入端加一个小的电压。这个需要加的小电压即为输入失调电压Vos。 运放内MOS不平衡导致 补偿设计

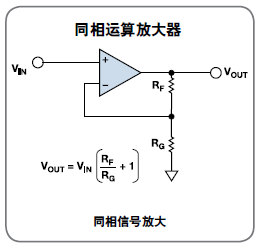

因为运放的高输入阻抗而虚断, 因为负反馈和极高的开环增益而引起虚短路。

输入偏置电流和输入失调电流

输入偏置电流Ib:是由于运放两个输入极都有漏电流的存在。实际的运放, 会有电流流入运放的输入端的。 那么输入偏置电流就定义这两个电流的平均值。

输入失调电流 Ios: 定义为两个差分输入端偏置电流的误差。输入失调电流同样反映了运 放内部的电路对称性,对称性越好,输入失调电流越小。

转化成失调电压,运放误差

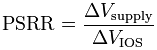

电源抑制比 (PSRR)

Power Supply Rejection Ratio

主要说明运算放大器对电源电压变化的抑制效果。 PSRR 的定义是每伏电源电压变化的失调程度,单位通常为微伏每伏 (uV/V)

越大越好db;有时候是反过来的,这时小一点更好 (uV/V)

越大越好db;有时候是反过来的,这时小一点更好 (uV/V)

随频率变化: 纹波噪声频率越大,PSRR越差

应用: 手持的小板面,LDO功耗大,散热多,效率低 像手环DCDC即可 但模拟信号处理不便,微弱信号放大 甚至与几M的信号没有抑制效果 方法 串电阻:全频带衰减 DCDC,尽可能减小纹波 滤波 穿心电容,理想LC滤波 其中一条曲线表示正电源变化时电路的PSRR表现(PSRR+),而另一条表示负电源变化时的表现(PSRR-)。

CMRR

定义:差模电压增益与共模电压增益的比值

同样反应到输入失调电压

Vcm是共模电压变化

或者CMRR(dB)=20lg(Ad/Ac)

或者CMRR(dB)=20lg(Ad/Ac)

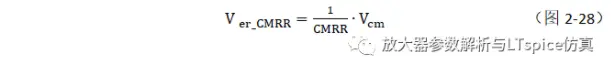

Vcm为输入共模电压,Ver_CMRR为共模电压所引起的输入直流误差

Vcm为输入共模电压,Ver_CMRR为共模电压所引起的输入直流误差

输入电容

环路不稳定:引入极点 共模输入电容Ccm和差模输入电容Cdiff。

环路稳定性因素: 频率 环路增益 ==相位裕量==:极点会导致相位裕量减小 一般有45度延迟,设计大于60度稳定 如果本来有80,在此处多了剪切频率,相位减少45度。只有35度,环路不稳定 +补偿电容并到反馈中改变相位

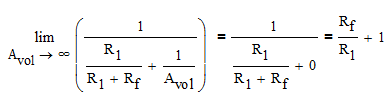

开环增益

理想的是无穷 现实中分布在数据手册给的区间内

闭环增益

增益带宽积

GBW:小信号(几百mV)下测的 大信号注意压摆率! 表格上是直流,图是交流

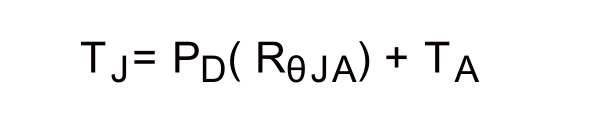

热阻

规范化:项目用到的IC的温升计算

芯片的核心:晶体管

芯片的接口:MOS管

结温就是PN结温度?,和封装有关,封装越小结温越大

热阻R单位为度/瓦,每一瓦引起的温升.

商业用环境温度:0-70度

Pd:手册中,资源使用评估,

热阻R单位为度/瓦,每一瓦引起的温升.

商业用环境温度:0-70度

Pd:手册中,资源使用评估,

目标:芯片工作在正常工作温度,考虑压力测试情况

测试时测外壳 温升太大考虑散热设计 国外芯片温度有裕量233,一般需要自己设计裕量

原厂芯片Demo:实现功能,测试芯片 实际应用:长时间,前后级,不能照抄demo,可以理解参考